摘要:本文对一种采用了FPGA设计方法进行建模仿真的交通控制器进行了详细介绍。为了满足智能交通控制器的需要,对各个子模块的建模设计思想、仿真验证子模块的设计正确性进行了分析,再将子模块整合成了顶层智能交通控制器,并通过软件来测试其设计的正确性。该智能交通控制器采用了EP3C10E144C8芯片。根据最后的结果表明,该智能交通控制器能够实现交通信号灯的控制以及的倒计时显示。

关键词:智能交通 控制器 建模仿真

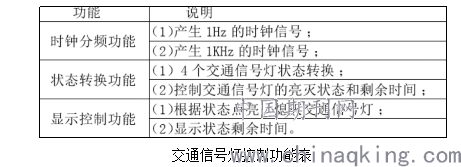

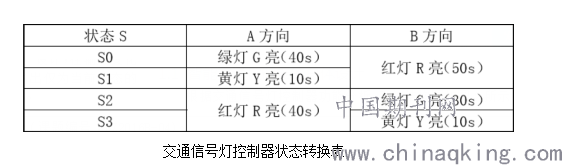

引言:随着我国社会经济的高速发展,城市轨道交通的建设也越来越快,智能交通控制器的发展也呈现出多样性的特点。FPGA的设计方法为在可编程逻辑器件内部进行硬件电器和功能的EDA设计,为电子智能产品的设计提供了新的发展方向,本文采用了FPGA设计方法进行了只能交通控制器的建模与仿真,设计出了一个具有3种信号灯和倒计时显示器的十字路口智能交通控制器的设计。在十字路口的A和B两个方向各设置一组信号灯,绿灯为G,黄灯为Y,红灯为R,A和B两个方向各设置一组倒计时显示器,处于A方向的绿、黄、红三种灯的显示时间分别为40S、5S、50S,B方向的三种灯分别为30S、5S、60S,交通信号灯是数字系统,每个相对的信号灯状态完全相同,并且具有表中的功能。

交通信号灯控制功能表

交通信号灯控制器状态转换表

一丶智能交通控制器的建模

(一)智能交通控制器的总体设计

根据智能交通控制器的功能分析,其结构如下图所示:

.png)

交通信号灯控制器的系统结构图

根据上图可得,串口通信接口的驱动中有3个板块

第一,时钟分频模块:用于产生1Hz秒的计数信号和1KHz的扫描时钟信号。

第二,状态转换模板:控制交通信号灯4个形态之间的切换,包括剩余时间和信号灯的切换。

第三,显示控制模板:控制信号灯的亮灭,显示时间的个位和十位1。

智能交通控制器的I/0端口如下图所示:

.png)

智能交通控制器的I/0端口说明

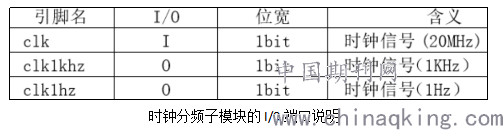

(二)时钟分频子模块的建模

时钟分频子模块的建模主要功能是产生1HZ的秒的计数信号和1KHz的扫描时钟信号,如下图:

.png)

时钟分频子模块符号

时钟分频子模块的I/0端口说明

时钟分频子模块的建模主要是将系统的始终转换成秒计数时钟,降低系统时钟来满足智能交通控制器中的倒计时读秒需要,这种转换就是分频器,其计算公式为:

根据已知,秒计数的时钟需要的分频倍数为20×106,对输出时钟每计数n/2个时钟周期,输出时钟就会翻转一次,从而产生秒计数,扫描始终的原理与秒技术始终的原理相通,但是其需要的分频倍数为20×103。

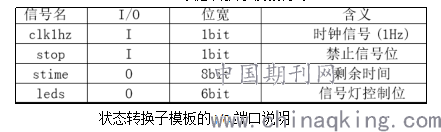

(三)状态转换子模板的建模

状态转换子模板的主要功能为完成A和B两个方向中四个状态的转换2。具体如下图:

.png)

状态转换子模板符号

状态转换子模板的I/0端口说明

智能交通控制器采用的是moore状态机进行的状态转换,其输出与当前状态息息相关,在时钟脉冲的有限个门延时后,输出逐渐稳定,即是该时钟的输入信号发生改变,其输出信号也不会发生改变,输入信号对于输出信号的影响要到下一个周期才能体现,信号的输入和输出分离是Moore的主要特征3。

(四)显示控制子模板的建模

显示控制子模板的主要功能是控制A和B两个方向的信号灯并且显示剩余时间,其符号具体如下图:

.png)

显示控制子模块符号

显示控制子模块I/0端口说明

显示控制子模块的建模思想为将BCD码换成7段数码管的位段显示码,一次来进行十进制的显示,比如数字为1,位段码则为06H,即为00000110B。

二丶智能交通控制器的仿真

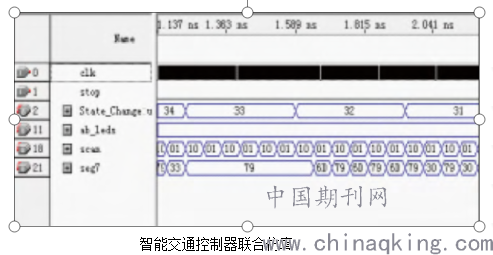

把时钟分频子模块、状态转换子模块、显示控制子模块整合为智能交通控制器。

智能交通控制器联合仿真

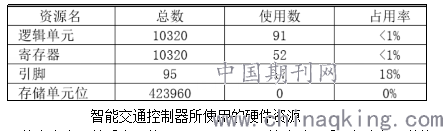

从上图可以看出,随着状态的变化,交通灯也在发生着不同的变化,不同交通状态的剩余时间也在发生着变化,并进行倒计时,完成智能交通控制器的设计,满足智能交通控制器的需求。智能交通控制器所使用的EP3C10E144C8的硬件资源具体如下图所示:

智能交通控制器所使用的硬件资源

从上表中可以看出,使用EP3C10E144C8芯片时,采用很少的硬件资源就可以实现智能交通控制器,借助Quartus设计软件能够很好的进行建模与仿真4。

三丶智能交通控制器的测试

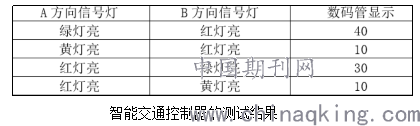

对建模设计完成的智能交通控制器进行控制正确的测试,其测试步骤首先是编写智能交通控制器的TestBench测试编码,然后在Mode1Sim工具中添加并编译通过的源文件,最后启动仿真,查看具体的测试结果。

智能交通控制器的测试结果

从测试结果中可以看出,结果没有出现差错,控制正确。A方向绿灯亮,车辆正常通行,经过40S后黄灯亮,10s后红灯亮,一共时间为50s,于此同时,B方向一直处于红灯状态,禁止车辆通行。当A方向是红灯亮时,车辆禁止通行,此时B方向绿灯亮,车辆正常行驶,30s之后黄灯开始亮,10s后红灯亮,B方向禁止通行,一共用时40s5。

结束语:该智能交通控制器采用了FPGA的模块化设计理念,首先设计的是时钟分频、状态转换以及显示控制这三个子模块的模型,然后才是将子模块整合到顶层智能交通控制器 中,通过仿真,子模块功能均没有出现错误,整合后的智能交通控制器动作控制正确,说明智能交通控制器的建模正确。

参考文献

[1]唐敏.基于FPGA的智能交通控制器的建模与仿真[J].电子测试,2017,(6):13-16.

[2]邓人菠.基于FPGA的智能交通监控前端系统研究与设计[D].四川:电子科技大学,2013. DOI:10.7666/d.D769666.

[3]张卿,曹晓平.基于FPGA的智能交通信号控制器设计[J].山东工业技术,2017,(16):141. DOI:10

[4]谭会生.基于FPGA的网络通讯流量模糊控制器的实现[J].测试技术学报,2011,25(5):421-426.

[5]汪小会,高卫东.基于FPGA的多功能交通信号控制器设计[J].电气电子教学学报,2010,32(2):61-63.

作者简介:陈明,男,出生年月: 1968年3月,籍贯:湖南省双峰,民族:汉族,学历:本科,职称:工程师,研究的方向:交通控制、自动控制。